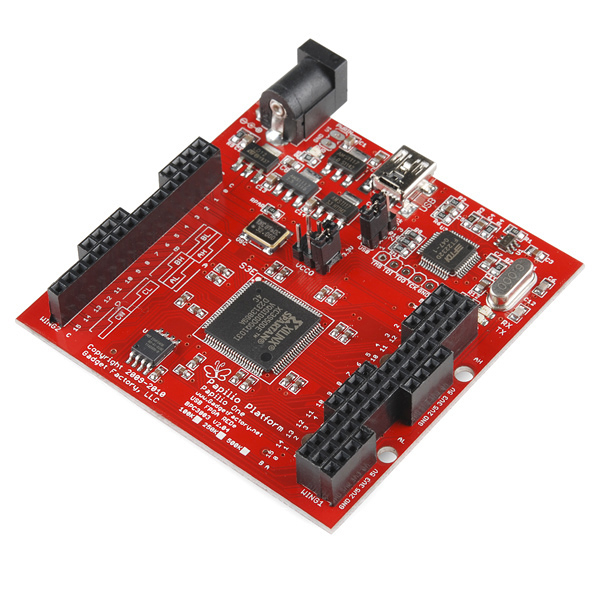

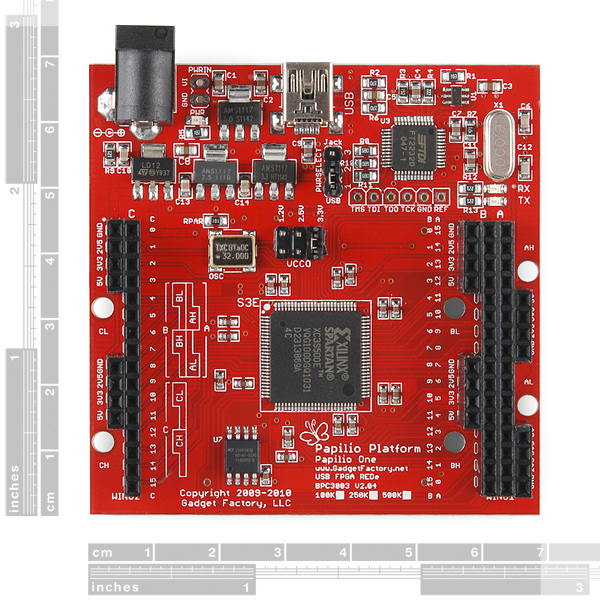

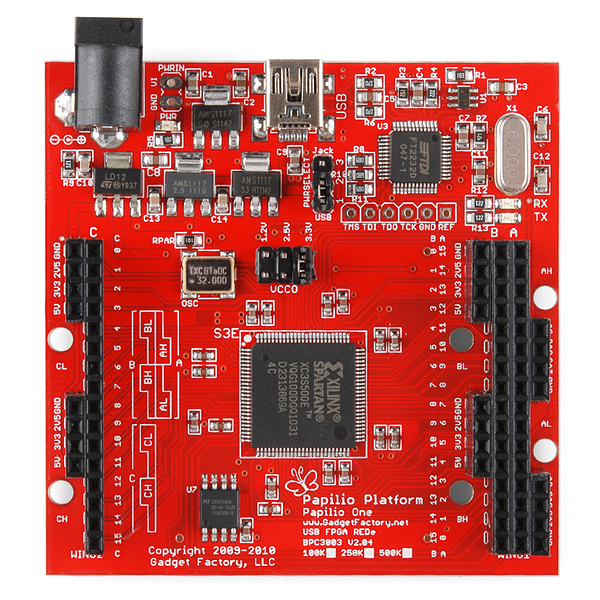

Papilio One - 500K

Are you interested in FPGA development but don't know where to start? Why not give Papilio a try? The Papilio One is an open-source development platform based on the capable Xilinx Spartan 3E FPGA. While FPGA devices are massively powerful and configurable, they haven't always been the easiest to develop. Papilio attempts to remedy this situation by following the lead of popular microprocessor development tools like Arduino. The Papilio One can be expanded by the use of "wings" which are stackable add-on modules, similar to Arduino shields.

You can still use traditional FPGA development tools to write code for the device. The Papilio isn't directly supported in Xilinx ISE but a script file is available on their website to load bitstreams generated by the program.

One unique feature of Papilio is that they provide a custom version of the Arduino IDE which allows to you write Arduino code and upload it to an AVR8 Soft Processor, an Arduino-compatible processor being emulated inside the FPGA!

- Fully Assembled with a Xilinx XC3S500E and 4Mbit SPI Flash Memory

- Provides an Easy Introduction to FPGA, Digital Electronics, and System on a Chip design

- Easily add New Functionality with Wings that Snap onto the Board

- Two-Channel USB Connection for JTAG and Serial Communications

- Four Independent Power Rails at 5V, 3.3V, 2.5V, and 1.2V

- Power Supplied by a Power Connector or USB

- Input Voltage (recommended): 6.5-15V

- 48 I/O lines!

Papilio One - 500K Product Help and Resources

Core Skill: Programming

If a board needs code or communicates somehow, you're going to need to know how to program or interface with it. The programming skill is all about communication and code.

Skill Level: Expert - You should be extremely comfortable programming on various hardware in several languages.

See all skill levels

Core Skill: Electrical Prototyping

If it requires power, you need to know how much, what all the pins do, and how to hook it up. You may need to reference datasheets, schematics, and know the ins and outs of electronics.

Skill Level: Rookie - You may be required to know a bit more about the component, such as orientation, or how to hook it up, in addition to power requirements. You will need to understand polarized components.

See all skill levels

Comments

Looking for answers to technical questions?

We welcome your comments and suggestions below. However, if you are looking for solutions to technical questions please see our Technical Assistance page.

Customer Reviews

No reviews yet.

I just want to reinforce what Member #257465 has said. If you are not a advanced FPGA user this board alone will do you very little good, its gonna sit their like a turd even if the code uploads due to its lack of on-board bells and whistles. Mike Fields, AKA Hamster has designed the LogicWing with a free tutorial (100+) pages witch is nothing short of excellent. I have fooled with other xilinx boards and the Papilio board with his logic wing along with his free book puts the other companies stuff to shame. SF really should sell the LogicWing with this board as a kit.

So are you saying that if you want to start learning FPGA (from somebody who only knows standard logic) that you should get this board AND this Hamster's LogicWing? Got a link for Hamster's LogicWing? Thanks

If anybody is looking for an intro to using Xilinx FPGAs with VHDL (I'm outside of the US, so I use VHDL...) have a look at

http://hamsterworks.co.nz/mediawiki/index.php/FPGA_course

It uses the same chip as on this board, and it will soon updated soon to include the Papilio One once Gadget Factory release the LogicStart MegaWing.

Is there some reason you have to use VHDL if you're outside the US?

For whatever reason, VHDL is more popular outside the USA. Either language will do what you want. VHDL syntax and structure is based on Ada while Verilog looks like C. You can use both languages in a design, but not in the same source file. So if you download a VHDL memory controller and Verilog CPU, they can be used in the same project.

Which is odd considering VHDL was a USG sponsored language. It takes from ADA, Pascal, and a few other languages of the day - but mostly from ADA (which is itself, a government language).

Verilog is much more C like and more familiar (syntactically) to developers. Although in practice Verilog behaves very much differently than C, at least the learning curve of understanding the syntax is lessened.

Maybe because Verilog is a newer language and the rest of the world has yet to catch up?

You can obviously use VHDL or Verlilog using any tool for this board. Hamster uses VHDL.

The Xilinx XC3S500E has 232 I/O lines. So why are there only 48 I/O lines on the Papilio One ?

Also, I've read all I could find about the Papilio One but I'm still not clear about using the I/O lines. Are they 5v (so that I can connect TTL) or are they the lower voltages ? I want to be able to use the Papilio One without the LogicStart Mega Wing.

The reason there are only 48 I/O lines available for use is due to the fact that the chip is in a CP132/CPG132 package. This package allows only 92 IO lines, many of which are most likely reserved for interfacing through the FTDI and any other additional resources the board has on it.

This is probably a silly question but will the LogicStart MegaWing (products/11879) work with the Papilio One? In its description it mentions requiring a Papilio Pro but the header footprints seem to be the same as the Papilio One 500K. Thanks in advance!

Never tried it, but I'd imagine it would work. You may have slight compatibility issues however

I just got my shiny new Papilio One the other day and it's just as advertised. I had my first bit file loaded up and running within 5 minutes after installing the loader. The loader install was easy, but there was a little warning about not having signed drivers. I'm super paranoid so I elected not to install the drivers, hoping it was just a typical FTDI chip which I already have drivers for. I plugged the cable in and after about 2 minutes of thrashing (which seemed a little excessive) it came up as a recognized device. This is on Win7 Ultimate so ymmv on other platforms.

The only complaint I have so far is the usb plug. It fits a bit loosely and has a lot of side to side play. I tried wiggling it and breaking the connection but was unable to with just minor wiggling, so it's probably not that big of a deal. Either it's not quite standard dimension or my cable is small, but since my cable fits well in other devices I have to say it's probably the plug on the board.

Oh, and the holes drilled for standoff don't account for COG so when I plug my cable in the entire board leans forward. That kind of defeats the purpose of the standoffs. If my board is going to short out the pins from the power barrel connector when it leans forward it's almost worse than not having any standoffs at all. I realize the barrel connector for the power is probably in the way of drilling standoff holes on all four corners, but I'm sure you guys can get creative and figure out a way :).

I was able to fasten my standoffs to a flat surface that prevents my board from tipping over (I basically crazy glued the posts to a flat, thin sheet of plastic) and everything is fine. This is by far the easiest FPGA platform I've worked with and I've worked with Xilinx (Spartan 3E), Lattice (MachXO dev board which is marketed as a CPLD but it's really a FPGA in CPLD clothing), and Altera (DE0 Nano). The helper scrips and pin assignment file are crucial to a successful synthesis. This is a GREAT package for beginners and experts alike.

I've got an old arcade game from fpgaarcade.com running on a Papilio and use it as a screen saver (powered over standby power from the USB) - left on 24x7 with no issues, so a complex design at modest frequencies uses well under 500mA.

However the regulator does get noticeable warm if I use it to drive all the segments of 4xSevenSeg and 8 LEDs at an eye-burningly bright 100% - but with maybe an extra 200mA of load it is pretty much what I would expect.

hmm I don't like the Power supply of this at all, a single TO-223 regulator without heatsink feeding 3 more regulators? if you put 15 volts into this that would limit the current to 200mA

you need to stay under 8V to get 800mA without overheating, but is that even enough to run anything more than a simple program on this?

Can I recommend you provide an option of ordering this with the headers already attached? I can tell you from experience that if you don't have a fairly good soldering set up you can easily botch the solder job. Hello burnt traces and uneven headers.

Here's my trick - get four 40 pin header strips (code PRT-00116) and use them to hold all the headers in place while you solder them. You could get away with one or two strips, but with four you can hold all the headers in place at the same time.

Your headers will be perfectly aligned and you can then use the pins to attack your projects to the Papilio.

I don't find these hard to solder at all. Consider them good easy practice :) I've never messed this kind of job up and I'm terrible at soldering

What is the clock frequency of this setup?

As sgrace replied, you would use the DCM. On the Papilio site there is a video tutorial on how to use the DCM. I suggest checking that out to get your head around clocks.

I also wanted to add, you definitely DON'T want to be creating your own clock manager or PLL. PLL's are very non-digital (they live primarily in analog land) and are very difficult to synthesize correctly. If you can't use DCM or a PLL, the best bet is to use clock enables. That way you clock your entire design with the same 32Mhz clock so there should be no skew. The clock enables enable operation on rising edge of the clock signal and prevents timing errors in your design.

FPGAs do not have internal clocks, and you have to give the FPGA a clock frequency to work with. IN this case, they are providing a 32MHz frequency to use. From here you can use features of the FPGA like a Digital Clock Manager (DCM) to adjust the clock to something more specific for your needs.

Consult documentation. In a case like this you would need to look at the Spartan-3 HDL Design Guide.

FPGAs don't have preset clock frequencies. Their speed depends on various propagation times as well as the precision required by the code they're running. That said, the P1 has a 32MHz oscillator that you can use as a reference for slower or faster clocks in your circuit.

So what's the difference (Other than the soft-core, the fact you can't easily synthesize, and 30 bucks) from the Spartan 3E breakout board? I've used the breakout board for about 2 years now and have nothing but good luck with it. It was plug and play with WebPack and I was able to synthesize simple models in less than an hour after I received it. This seems like you would have to jump through hoops to get something synthesize. So, in effect, it looks like an overpriced AVR8 breakout board. Or am I missing something? (By the way, I can synthesize the AVR8 core on the spartan breakout board as well).

You're missing the fact that this is targeted at beginners and non EE types. You don't jump through anything. I don't own one but I do own a small Altera board from knjn.com and it works in a similar manner, though its just plain old rs232. You use a vendor supplied program to upload the bit stream to the boot ROM. You cant debug but there is a jtag header so you can still program/debug it strait from ISE if you wanted.

Bottom line is this is like the Arduino, a low cost introduction platform. You are not its intended audience.

The breakout board doesn't have PROM to program the bitstream to for your FPGA to be persistent.

From there site:

I don't think it's necessarily a limitation unless you are wanting to do some Chipscope type debugging.

http://spritesmods.com/?art=stdalonejtag

this can replace the prom for some parts

Why do you guys not have the cheaper(ie, beginner friendly) 250K version?

Also, if you plan on getting this and programming it with VHDL or Verilog, this is a marvelous cheap device, but no matter what, Xilinix WebPack is an 8gig bloated piece of crap that will make any beginner give up on HDLs forever. I recommend instead using ghdl or other simpler tools for simulation and only when you actually need to test it on actual hardware, use WebPack. See also: electronics.stackexchange.com

250k FPGAs are on their way out, and this is VERY cheap for a 500k. Look at SFE's development board which is 100 bucks!

I am not going to deny that there are good open sourced compilers/debuggers/simulators and do what they can, but the BEST software out there always has a steep learning curve. But did you know that a lot of that stuff is based off the industry software like the Xilinx ISE Tools? I have tried Icarus for HDL in college, but it was cumbersome to install and use. It's MUCH easier to suck-up the 8GB install and use tools that are designed and tested on Linux AND Windows (sorry Mac users). Just remember the industry software is for professionals, not hobbyists. Besides, Xilinx provides tutorials for their software AND they have a Documentation Navigator that has EVERY SPECIFICATION DOCUMENT THEY PRODUCE!

FPGA development is very difficult to someone who has not had been classically trained (courses/colleges). By using an industry software that provides a FREE version for people to use makes things easier. Their support forums are great with a lot of contributors. The other thing is, FPGA stuff is not cheap, period.

I recommend to new users to suck up and buy a reference book to use. I recommend this one: http://www.amazon.com/Digital-Design-Edition-Morris-Mano/dp/0131989243/ref=ntt_at_ep_dpt_3

I find Mano's style of writing to be perfect for someone who has never done digital logic before (I still reference him in my designs). Yes the book is expensive, but worth it's weight in gold if you do FPGA development.

I agree with everything you said here except for the fact that the 250k gate version is perfectly adequate for 98.6% of your users. Mike fields (aka Hamster) has large designs (i.e.Synth) in VHDL that get no where close to using the number of gates available on the cheaper chip.

Not sure why 250K would be more suitable than the 500K... All I was stating was the older generation of FPGAs Xilinx offers are on their way out. They are at the 180nm node, and most foundries don't even have 180nm node equipment anymore.

Also, to do more advanced things on the FPGA requires a much bigger chip. Most people will not need more than 250K, but there are times when 250K is not going to work. As an example, look at the Bitcoin FPGA minors out there. They all use a Spartan6 LX150, why? Because it is big enough for the SHA256 hashing core, plus some control signals. Can a Spartan3E or Spartan3A do a SHA256 core? Yeah, but you'd be stuck with nearly 80% of the chip used, and at 80% of the chip being used turns into a routing nightmare and the chance of the design being used will only decrease.

Here's an example of a large design I used on a Spartan3. In college I wrote a game of Pong on the FPGA. We originally were going to use the Coolrunner 2, but we utilized too much, so we went with the Spartan3E. Our design was 60% utilizing the chip. Know what the biggest part of the design was? VGA out at 640x480. What if we had it output at a higher resolution? More of the chip would be utilized.

So, I'm not sure why 250K is superior, to you (I'm assuming), than a 500K. They both are the same thing, just one is bigger.

Put your VGA frame buffer in external ram and write a dram module. Make sure you design in DMA for the dram module so the VGA module doesn't have to eat up CPU time reading the frame buffer. That will save you a LOT of LUT's with the 640x480 RAM gone.

There is also another nice program for developing both Verilog and VHDL code call Active HDL by Aldec. Its a professional tool but they do offer a free (but limited) student edition that does not require student verification. Just sign up for the free student edition and you get a download link via email. Its windows only though :-( http://www.aldec.com/en/products/fpga_simulation/active-hdl

But I agree ISE is a visual mess, the interface is clumsy. I always felt more comfortable in Quartus II. There should be more low cost Altera devices on the market.

I've got a cheapo one I've been developing.. Still gotta verify the config IC works with the board. Alternatively, Terasic has a pretty nice cheapo Altera board (de0-nano) for $80. It looks like a very nice board to start up with for beginners. I second Quartus II is a nice tool to work with. Pretty smooth sailing there from my experience.

I'm assuming Quartus II doesn't work with these chips? I've never done FPGA, but it interests me.

Quartus is the house Altera FPGA only tool, just as ISE is the Xilinx only house tool. This wont ever change. Third party tools are available from the big 3 (Cadence, Synopsis, Mentor Graphics) but start at thousands of dollars.

The Lattice and Mircosys/Actel also have their own FPGA free version house tools. Also as SGrace has pointed out, I wouldn't even consider using open-source tools at this point with FPGA's, very little chance you are going to generate a remotely viable bitfile.

So for somebody wanting to dip a toe into the FPGA area with as little brain-strain (learning curve) as is possible with such complex stuff, what would you recommend? From comments here, Quartus II sounds like it might be the go, but everybody has their own ideas and experiences. I know plain digital logic and have done a little with old PAL/GAL stuff with the old PALASM, but haven't done any Verilog or VHDL.

Hi Sleep,

There is a C/Processing/Arduino based IDE for this Papilio One board. I haven't played with many coding examples for it through this IDE yet. However I would highly suggest you buy the Papilio board and buy The LogicStart Megawing. That particular wing comes with a free FPGA book and VHDL tutorial. You can follow it and program the board even if your HDL knowledge isn't good using the free Xilinx WebPack ISE. Its the easiest board I have ever used when combined with Mike Fields(Hamsters) book and wing.

Having said that, your FPGA Language choices are pretty much VHDL/Verilog/SystemVerilog/SystemC whether you go with Xilinx's ISE or Altera Quartus. Programming FPGAs is still in the explicit, low level state compared to MCU's but that is slowly changing as resources and chip real estate becomes cheaper. Eventually FPGA semantics will closely resemble higher level programing code, just not yet.

Thanks for all that info, quite helpful. Yes I understood there was the Arduino like IDE, though I couldn't see a lot of point in learning what seemed like just a soft Arduino, if it didn't do anything else, might as well use a physical one - perhaps there's more to it that I'm not seeing? Anyway, I've downloaded Hamster's book and found the wing, so thanks for the advice :)

Hey Sleep, No you are exactly right, you have the option of coding HDL directly through the ISE Webpack, or c-style through the FPGA/Arduino IDE interpreted to the softcore processor.

Ive also been playing lately with the inexpensive DEO-Nano from Terasic. Its pretty cool as well. For that board you Use Alteras Quartus-II.

You can also use C/C++ style coding through the Xilinx SDK or Altera Nios. They both provide Eclipse customized plug-ins for their emulated soft-cores (Microblaze, AVR etc.). I cant speak to licensing cost issues on those products

I believe Aldec's free Active HDL is a front-end wrapper that still requires a Xilinx or Altera EDA engine for Synthesis. Also their interface seems outdated with its look and feel and half the functionality is disabled. I agree with SGrace for this board, use the Webpack and deal with the learning curve.

does the AVR8 softcore allow adding custom IO modules?